| Quantity | 3+ units | 10+ units | 30+ units | 50+ units | More |

|---|---|---|---|---|---|

| Price /Unit | $28.39 | $27.81 | $26.94 | $25.78 | Contact US |

5-Wire DC Brushless Fan Testing Board with Storage Box for Internal and External Fan Detection

$25.23

5-Wire DC Brushless Fan Testing Board with Storage Box for Internal and External Fan Detection

$25.23

New 5000W Pure Sine Wave Inverter Board Motherboard 5KW Over-load Protection (Precharge DC320-500V)

$108.99

New 5000W Pure Sine Wave Inverter Board Motherboard 5KW Over-load Protection (Precharge DC320-500V)

$108.99

OpenCV OAK-D-Pro Camera Module AI Embedded Machine AI Vision Kit for Depth Measurement/Image Recognition

$587.21

OpenCV OAK-D-Pro Camera Module AI Embedded Machine AI Vision Kit for Depth Measurement/Image Recognition

$587.21

WCH CH565W-EVT High Quality Evaluation Board Ultra High Speed USB3.0 Built-in PHY RISC-V3A without Optical Module

Description:

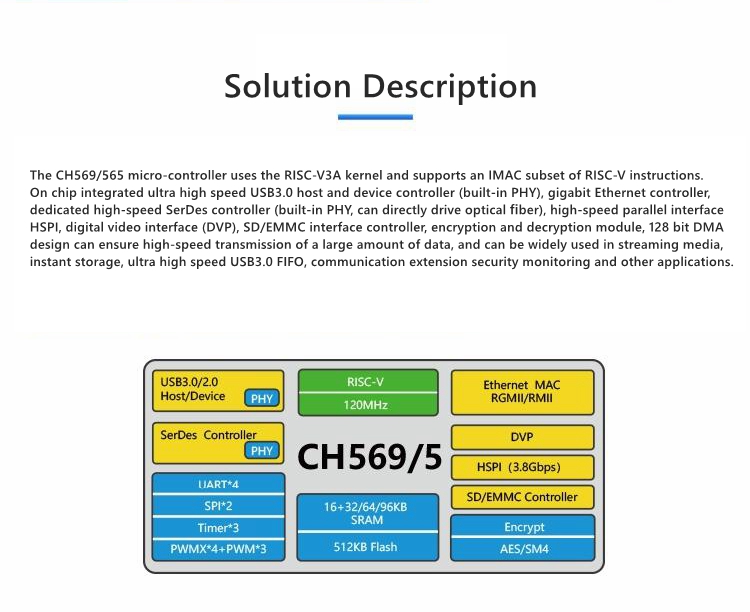

- The CH569/565 micro-controller uses the RISC-V3A kernel and supports an IMAC subset of RISC-V instructions. On chip integrated ultra high speed USB3.0 host and device controller (built-in PHY), gigabit Ethernet controller, dedicated high-speed SerDes controller (built-in PHY, can directly drive optical fiber), high-speed parallel interface HSPI, digital video interface (DVP), SD/EMMC interface controller, encryption and decryption module, 128 bit DMA design can ensure high-speed transmission of a large amount of data, and can be widely used in streaming media, instant storage, ultra high speed USB3.0 FIFO, communication extension security monitoring and other applications.

Features:

- RISC-V core, 120MHz system MCLK, support single-cycle multiplication and hardware division, programmable interrupt controller, low-power two-stage pipeline.

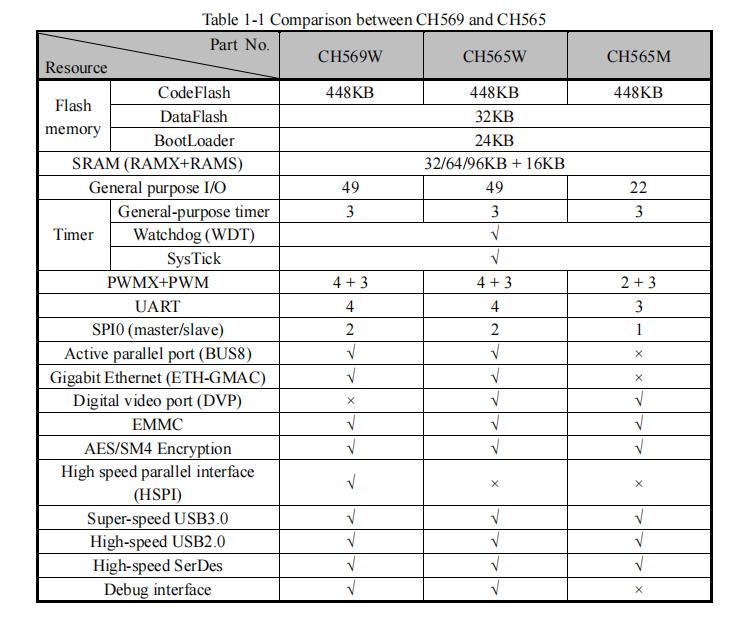

- 448KB CodeFlash, 32KB DataFlash, 16KB 32-bit SRAM, 32/64/96KB configurable 128-bit SRAM.

- Built-in ultra-high-speed USB3.0 control and transceiver (built-in PHY), support USB3.0 Host/Device mode, OTG function, support USB3.0 HUB.

- Built-in high-speed USB2.0 control and transceiver (built-in PHY), support USB2.0 Host/Device mode, support control/batch/interrupt/synchronous transmission

- Built-in Gigabit Ethernet controller (Ethernet), providing RGMII and RMII PHY interfaces, supporting 10/100/1000Mbps transmission rate.

- Built-in digital video interface DVP, configurable 8/10/12-bit data width, support YUV, RGB, JPEG compressed data.

- Built-in high-speed parallel interface HSPI, configurable 8/16/32-bit data width, built-in FIFO, support DMA, the fastest transmission speed is about 3.8Gbps.

- Built-in SerDes control and transceiver (built-in PHY, can directly drive optical fiber), support network cable (only use 1 set of differential lines) transmission of 90 meters, support 1.25Gbps high-speed differential signal communication.

- Built-in EMMC controller, support single-wire, 4-wire, 8-wire data communication mode, in line with EMMC card 4.4 and 4.5.1 specifications, compatible with 5.0 specifications.

- It supports AES/SM4 algorithm, 8 combined encryption and decryption modes, and supports SRAM/EMMC/HSPI peripheral interface data encryption and decryption.

- 4 groups of UART, maximum baud rate 6Mbps, compatible with 16C550, built-in FIFO, multiple trigger stages.

- 2 groups of SPI interfaces, support master/slave mode, built-in FIFO, support DMA.

- Active parallel port: 8-bit data, 15-bit address bus.

- 3 sets of 26-bit timers supporting timing, counting, signal catch, PWM modulation output, 4 groups of extended PWM outputs with adjustable duty cycle.

- 49 general-purpose I0s, 8 programmable level/edge interrupts, and some pins have multiplexing and mapping functions

- Built-in watchdog, integrated 2-wire debugging interface, support online simulation.

- Support low-power mode, support part of GPIO, USB, Ethernet signal wake-up.

- Chip ID No.: unique 64-bit ID identification number.

Instruction:

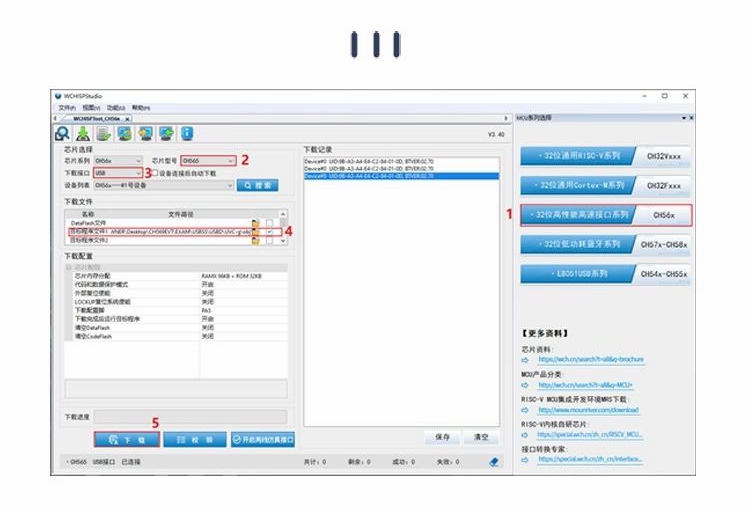

- Please download the WCHISPTool.exe tool from the website (https://www.wch-ic.com/) to download the hex file to the chip flash. The CH565W chip needs to enter download mode in order to use ISP tools to download the code, and generally using USB is the most convenient way to download the code. The CH565W chip will enter download mode when it detects two situations when powered on: firstly, it detects that the first 16 bytes of the flash are 0xff, and secondly, it detects that the boot pin is at a low level. If the chip does not communicate with the ISP tool within 10 seconds after entering download mode, it will automatically exit download mode. Connect the CH565W evaluation board to the computer using a USB plug. As shown in the figure, open our official ISP download tool, select CH565/CH569 chip signal, USB download method, power off the CH565W evaluation board, and then press and hold the download button on the evaluation board to power on. At this time, the USB device list of the ISP tool will display the newly connected CH565W chip.

- Select "Run target program after download" and "Enable RST pin as manual reset input pin" as needed, select the compiled .hex file in the user program file bar, and finally click "Download" to download the program to the master chip on the evaluation board and automatically run it. Before powering on the CH569W chip, connect the HDO pin to the GND pin, and enter download mode after powering on. After downloading the program, disconnect the HDO pin from the GND and power it on again.

CH569/5 Data Sheet Download:

- https://www.wch-ic.com/downloads/CH569DS1_PDF.html

CH569/5 Official Routines:

- http://www.wch.cn/downloads/CH569EVT_ZIP.html

Routines:

- BUS8: BUS8 Operation CH372 Routine

- DVP: OV2640 Camera Operation Routine

- ECDC: ECDC Routine

- EMMC: EMMC Routine

- ETH-GMAC: GMAC_RAW: Ethernet raw data transmission routine/ TCP_Client: TCP client routine/ TCP_ Server: TCP server routine/ UDP: UDP routine

- FLASH: Erase/read/write routines for FLASH

- GPIO: GPIO Routines

- HSPI: HSPI burst mode upper and lower transceiver routines/HSPI burst mode. Switching between upper and lower transceiver routines/HSPI dual DMA mode, hardware automatic response mode upper and lower transceiver routines/HSPI upper and lower transceiver data encryption and decryption routines/HSPI normal mode upper and lower transceiver routines

- PWMX: PWMX Routine

- SPI: SPI0 operation external FLASH routine/SPI0 host routine/SPI0 slave routine/SPI1 host routine/SPI1 slave routine/SPIx using DMA, host slave transceiver routine

- TMR: Timer function routine

- UART: UART transceiving routine

- USBSS: Simulate custom USB device (CH372 device) routines/UVC device routines/simple enumeration process routines for USB devices/USB file system examples

Package Included:

- 1 x CH565W-EVT Evaluation Board